Metodologías de optimización para circuitos nano electrónicos con variaciones de proceso

DOI:

https://doi.org/10.33017/RevECIPeru2017.0013/Palabras clave:

Variaciones de proceso de fabricación de C.I., variaciones estadísticas, retardo, tecnologías nanométricas con CMOS, correlaciones estadísticas, velocidad de subidaResumen

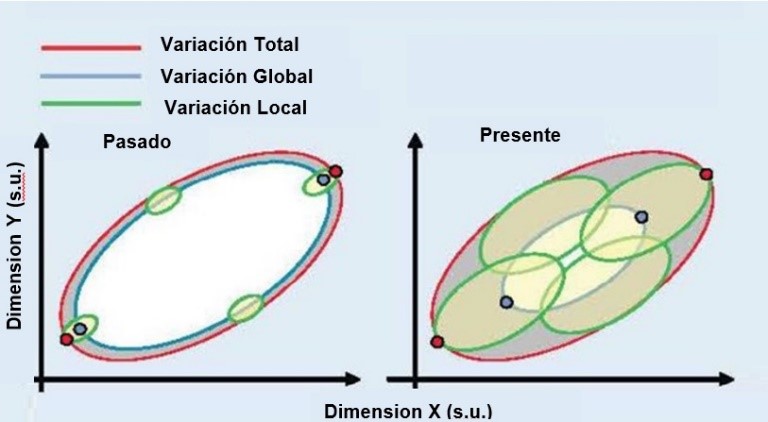

El escalamiento que se viene produciendo como parte del desarrollo tecnológico en el diseño de los circuitos integrados electrónicos ha generado la necesidad de considerar como elemento significativo las variaciones que se producen en las características del circuito como consecuencia de las variaciones en el proceso de fabricación, debido a que los diseños de sistemas electrónicos actuales son implementados en tecnologías nanométricas, en donde son muy significativos los efectos e influencia de dichas variaciones [1] [2].Además las exigencias de mejores comportamientos en velocidad y consumo de potencia, conlleva a incorporar la optimización de estas características, como un requerimiento en la metodología de diseño. En este artículo se presentan dos metodologías propuestas para el diseño de circuitos integrados electrónicos modernos, metodologías que tienen por objetivo optimizar la velocidad de respuesta de los circuitos integrados, mediante la minimización de los retardos. Se presentan resultados de la aplicación de estas metodologías en circuitos estandarizados, una de ellas se denomina “el método de paso simple” y la otra “el método de paso múltiple”, en forma complementaria en las aplicaciones evaluamos el consumo de potencia dinámico. Se implementan algoritmos que están fundamentados en la teoría matemática de optimización de funciones [3][4].