Metodologías de optimización para circuitos nano electrónicos con variaciones de proceso

DOI:

https://doi.org/10.33017/RevECIPeru2017.0013/Keywords:

Manufacturing process variations of C.I., statistical variations, delay, nanometric technologies with CMOS, statistical correlations, slew rateAbstract

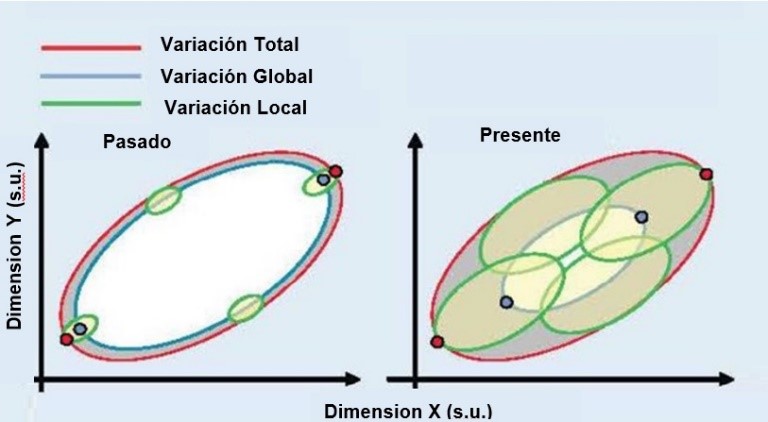

The scaling that has been taking place as part of the technological development in the design of electronic integrated circuits has generated the need to consider as a significant element the variations that occur in the characteristics of the circuit as a consequence of the variations in the manufacturing process, that the designs of current electronic systems are implemented in nanometric technologies, where the effects and influence of these variations are very significant [1] [2]. In addition, the demands of better behaviors in speed and power consumption, lead to incorporate the optimization of these characteristics, as a requirement in the design methodology. This article presents two proposed methodologies for the design of modern electronic integrated circuits, methodologies that aim to optimize the response speed of integrated circuits, by minimizing delays. Results of the application of these methodologies in standardized circuits are presented, one of them is called “the simple step method” and the other “the multiple step method”, in a complementary way in the applications we evaluate the dynamic power consumption. Algorithms are implemented that are based on the mathematical theory of function optimization [3] [4].